線上影音

Home > ANSYS SIwave教學> High Speed Differential Pair Optimized Design

本文始於2015,旨在介紹高速差動訊號對的設計要點。The article started in 2015, and it introduced some points and tips for a high-speed differential pair design.

![]()

初次接觸高速訊號或DDR設計的人,可以找到一些在談走線繞等長的舊資料(當中不乏過去大廠的design guide),但近幾年一些DDRII(或更快)的design rule,漸漸改以定義setup time, hold time budget with jitter取代length-matching routing rule,並且改以強調對時序圖的理解與使用模擬(margin predict)的重要性。簡單說:rule就是不管你怎麼layout設計,但時序要 設法滿足規格(timing margin),或傳輸線的損耗要在規格內。

線長差異只是影響時序的因素之一,stack-up\via\stub\coplane\slot\coupling...這些因素在高速訊號設計裡,在PCB與package level,彼此是有不同程度的交互影響,如果只是一味的要求蛇線等長,而讓走線的總線長大幅增加,蛇線本身引入的阻抗彎折處的不連續性與相鄰線間的寄生效應變大,這反而對高速訊號的設計是非常不利的,未蒙其利,先受其害。

1.1 繞蛇線的間距 [1]

Spacing有些文件是建議15~20mils、有些是3W、有些是6H...,但若考慮物理意義來說,筆者覺得以相對於堆疊高度的定義6H較好 ,或是沿用大師的說法:對於特性阻抗為50 ohm的傳輸線,使用3W rule。請注意,這樣的敘述方式其實就已經把疊構高度與線間距的關係確定下來了。

1.2 螺旋型蛇線效果較好 [2]

1.3 差動對繞蛇線的原則

蛇線盡量集中在產生線長差異的那一端,主要是為了 讓兩條線上傳遞的訊號緣,盡可能沒有時間差,也可保有差動對可以抗CM noise的物理特性

2.1 在蛇線間插入兩端點接地的guard trace, 可以降低50%的crosstalk. (接地via兩端放就夠) [3]

雖然這觀念蠻直覺的,但實作上因layout空間有限,蛇線間隙塞不下兩個grounded via,故少有這樣的作法

蛇線間穿插了guard trace而導致特性阻抗降低,這部分可以透過縮減訊號線線寬來補償回來。

2.2 在蛇線間插入只有一端接地的guard trace,另一端是open stub. [4]

這樣的效果跟放兩個接地via幾乎是一樣的Fig.5,這就有實用性了。

在guard trace兩側的蛇線間的crosstalk大部分會互相抵消as Fig.10(c) and Fig.12。

原因是這種結構下,接地端的反射係數是-1,open端的反射係數是+1,所以在0~1Td,g時間內產生的coupling noise Vn1經過 一次反射後會變成-Vn1,在1~2Td,g經過二次反射後會變成-2Vn1,會與在1~2Td,g才剛產生的coupling noise Vn2經過一次反射後的2Vn2"大部分"會抵消

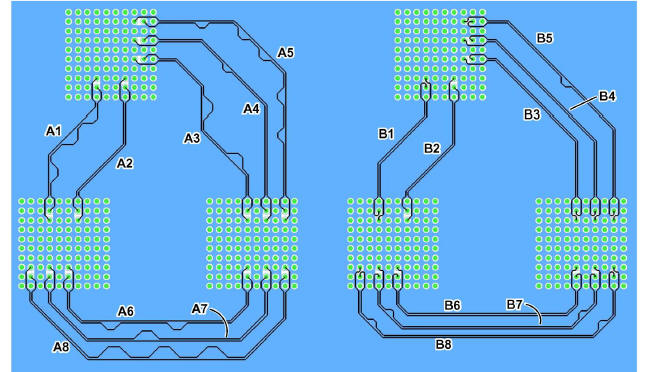

左邊(in-line)是差動對走線在進入BGA pin array之前,就先把長度匹配的問題調整好了;右邊(back-jog)是差動對走線利用在BGA array內的些微空間作轉折調整長度差異;後者效果較好(尤其在15G以上)。

-

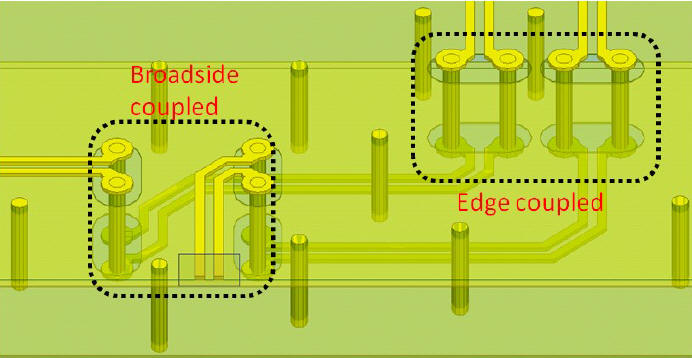

相鄰差動對的耦合降低 [6]

對於boardside coupling,可以透過某個角度的offset來降低耦合

而這耦合量最小的offset角度,其實就是從boardside coupled轉edgeside coupled的過渡位置

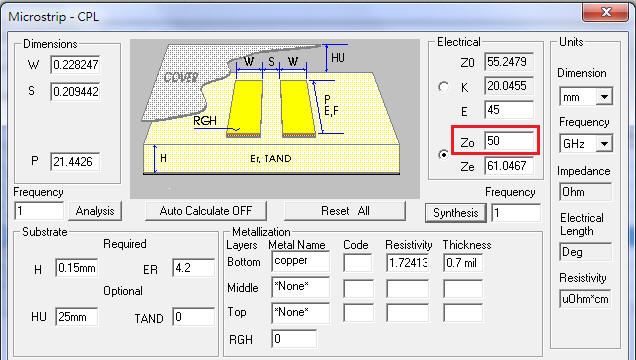

5.1 W=0.228mm, S=0.21mm, H=0.15mm, Er=4.2.

Zdiff=2*Zo=100 ohm.

Ref. differential and odd-mode impedance

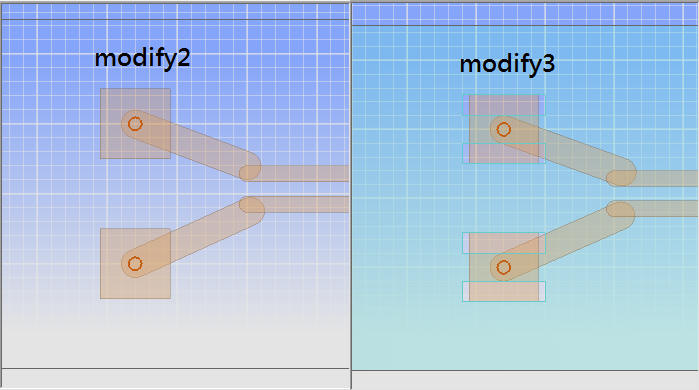

5.2 SIwave R16 example as below

5.3 TDR的step function由上圖的右側饋入

10~120ps為何TDR會震盪,請參閱問題與討論8.1。 TDR在250ps處的嚴重下凹是pad處的電容造成的,請參閱問題與討論8.2。

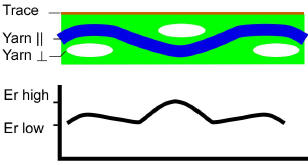

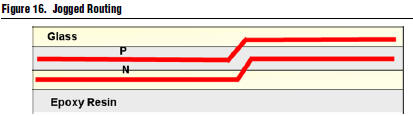

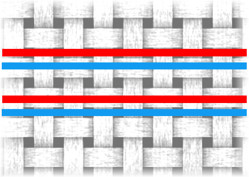

傳統上PCB的介電層是以玻璃纖維編織,再以環氧樹酯包覆而成。

宏觀上一般以固定的(constant)相對介電係數來表示其特性,比方e=4.4@1GHz,但對於數GHz的高速差動訊號來說,如果走線是沿著玻璃纖維編織方向呈0或90o,這時差動對個別正負訊號的特性阻抗會因為電場流動的路徑上,在微觀所感受到介質結構(特性)不同而不同。

如下圖所示,以上方側的差動對訊號線為例說明:藍色線下方區域都有玻璃纖維編織,而紅色線下方則除了玻璃纖維外,還有環氧樹酯。也就是藍色線受玻璃纖維的介電係數影響為主,紅色線還受環氧樹酯的介電係數影響,兩者的介電係數完全不同,這會造成差動對訊號線彼此間的特性阻抗與傳遞時間延遲不匹配,進而影響到眼圖。[7][8]

雖然weave effect只對於非常高速與很長的差動訊號有影響,但實際情況是,weave effect會多少吃掉一些design budget,降低design margin。[8]

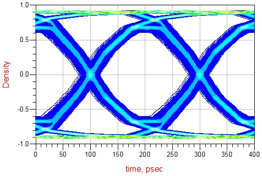

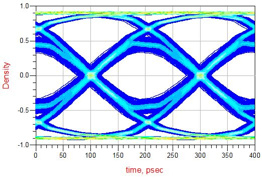

Eye Diagrams: Dielectric constant =4.5 versus dielectric constant of 4.2 (P) & 4.8 (N)

Trace length: 300mm, Data rate: 5Gbps, 100,000 bits including jitter.

Solution:Offset traces by the intra-pair spacing forcing each trace onto the path that its neighbor was on irrespective of the glass pitch. [9]

7.1 差動對的蛇線於180o轉彎處,內圈與外圈的線長不同,這在本質上就會引入共模成份。[10]

如果差動對的蛇線設計上,彎折的段數(N)能取奇數,也就是讓左右彎折的次數能相同(總數是偶數),那就能讓差動對的蛇線設計得到最小的differential-to-common mode |Sc2d1|.

另外,如果每段蛇線彎折的線段長度相同l=l2(symmetry),那也可以得到比較好的特性

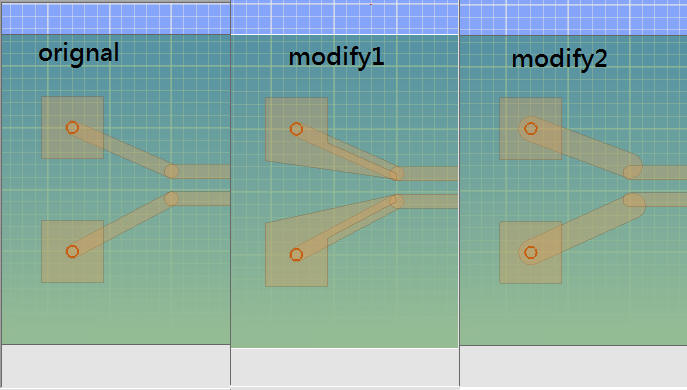

7.2 透過線寬縮減,改善差動對蛇線彎折處的TDR,與|Sc2d1|。[11]

7.3 同樣是在差動對蛇線彎折處想方設法改善特性,這次透過換層+縮減線寬,得到更好的效果 as Fig14, Fig15. [12]

[10][11][12]都是在討論差動對的蛇線特性與改善方法,由淺顯直覺的角度切入,一路打蛇隨棍上,開始看似單純的研究主題,但作者以細膩與嚴謹的手法,最後呈現出來是令人驚豔的成果。這樣做研究的精神與手法, 筆者深感敬佩,是我們要好好學習的。

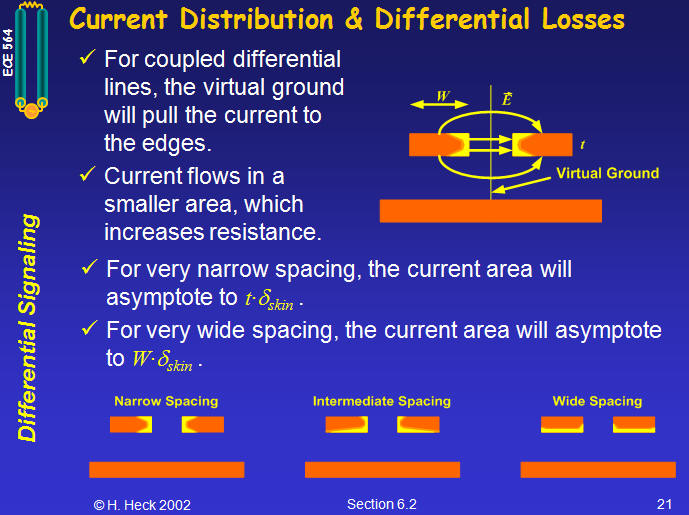

differential space越近,低頻loss會增加

這現象在SI領域稱為[Differential Loss],是因為近距離下,差動訊號間的電場強耦合所引起的肌膚效應,使得conductor loss增加的原故。[14]

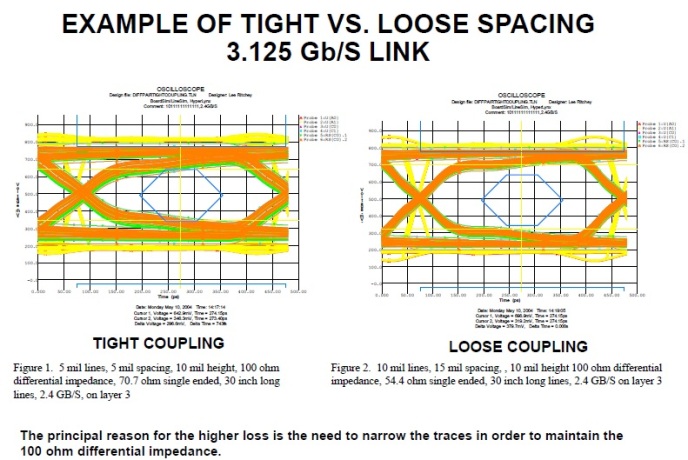

當維持100 ohm差分特性阻抗設計的傳輸線彼此距離愈近,其走線線寬勢必越小,所以低頻阻抗增加 [15]

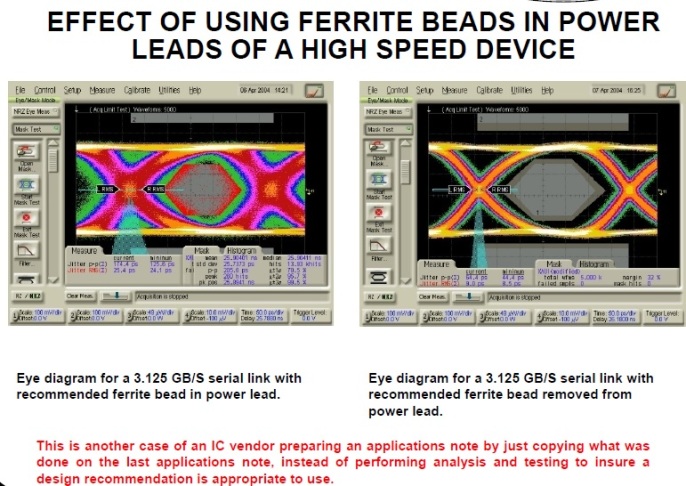

由於power bead會抑制電流瞬間充放電,可能影響高速IO的高頻響應行為,讓眼圖變差。所以就算design guide叫你加,也請謹慎驗證後才加。[15]

如果加power bead會影響眼圖,不加它power noise又過大,比較好的PI優化方法是加de-cap。

-

問題與討論Q&A

10.1 為何5.3圖的differential TDR在100 ohm附近一直震盪?

Ans:這是SIwave內一開始設定的模擬頻寬不夠所致,把extraction頻寬從20G加大到30~40G就沒問題了。

10.2 本文5.3圖在150ps處因為pad電容所造成的TDR大幅下降有辦法改善嗎?

Ans:如下圖右所示,把pad下方的參考地挖掉一些,但不要挖到trace下方的地。

有好的工具,做研究與創新一點都不難 。

[1] Howard Johnson, Martin Graham, High-Speed Signal Propagation: Advanced Black Magic, Prentice Hall PTR, 2003, ch. 12.8.4 .

[2] Wei-Da Guo, "Comparisons Between Serpentine and Flat Spiral Delay Lines on Transient Reflection/Transmission Waveforms and Eye Diagrams," IEEE Trans. Microw. Theory Tech., vol. 54, no. 4, pp.1379-1387, Apr. 2006.

[3] Guang-Hwa Shiue, "Guard Trace Design for Improvement on Transient Waveforms and Eye Diagrams of Serpentine Delay Lines," IEEE Trans. Adv. Packag., vol. 33, no. 4, pp.1051-1060, Nov. 2010.

[4] Guang-Hwa Shiue, "Improvements of Time-Domain Transmission Waveform and Eye Diagram of Serpentine Delay Line Using Open-Stub Type Guard Traces in Embedded Microstrip Line," IEEE Trans. Compon., Packag., Manuf. Technol., vol. 1, no. 11, pp.1706-1717, Nov. 2011.

[5] Michael J. Degerstrom, "Practical Design Considerations for Dense, High-Speed, Differential Stripline PCB Routing Related to Bends, Meanders and Jog-outs," p.27-36, DesignCon2014.

[6] Kunia Aihara, "A novel method to reduce differential crosstalk in a high-speed channel," DesignCon2015.

[7] oldfriend, "PCB glass-fiber laminate weave effect", 網際星空_電子站

[8] Signal Integrity Analysis \ Fiberglass Weave Effect

[9] "PCB Dielectric Material Selection and Fiber Weave Effect on High-Speed Channel Routing," p.17-19, Altera AN528, 2011

[10] Guang-Hwa Shiue, "Analysis of Common-Mode Noise for Weakly Coupled Differential Serpentine Delay Microstrip Line in High-Speed Digital Circuits," IEEE Trans. Electromagn. Compat., vol. 54, no. 3, pp.655-666, Jun. 2012.

[11] Guang-Hwa Shiue, "Common-Mode Noise Reduction Schemes for Weakly Coupled Differential Serpentine Delay Microstrip Lines," IEEE Trans. Compon., Packag., Manuf. Technol., vol. 3, no. 6, pp.1016-1027, Jun. 2013.

[12] Guang-Hwa Shiue, "Significant Reduction of Common-Mode Noise in Weakly Coupled Differential Serpentine Delay Microstrip Lines Using Different-Layer-Routing-Turned Traces," IEEE Trans. Compon., Packag., Manuf. Technol., vol. 4, no. 10, pp.1671-1683, Oct. 2014.

[13] High Speed PCB Design Rules 以純layout技巧,處理高速訊號設計的11個rules,對layout engineer蠻好的教學影片

[14] Howard Heck大師的講義(p.22,37~42)

[15] Santa Clara, "A TUTORIAL ON VERY HIGH SPEED DIFFERENTIAL SIGNALING", DesignCon2018, p20~23, p27~28.